- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC18F4539T-I/ML (Microchip Technology)IC MCU FLASH 12KX16 EE A/D 44QFN

2002 Microchip Technology Inc.

Preliminary

DS30485A-page 161

PIC18FXX39

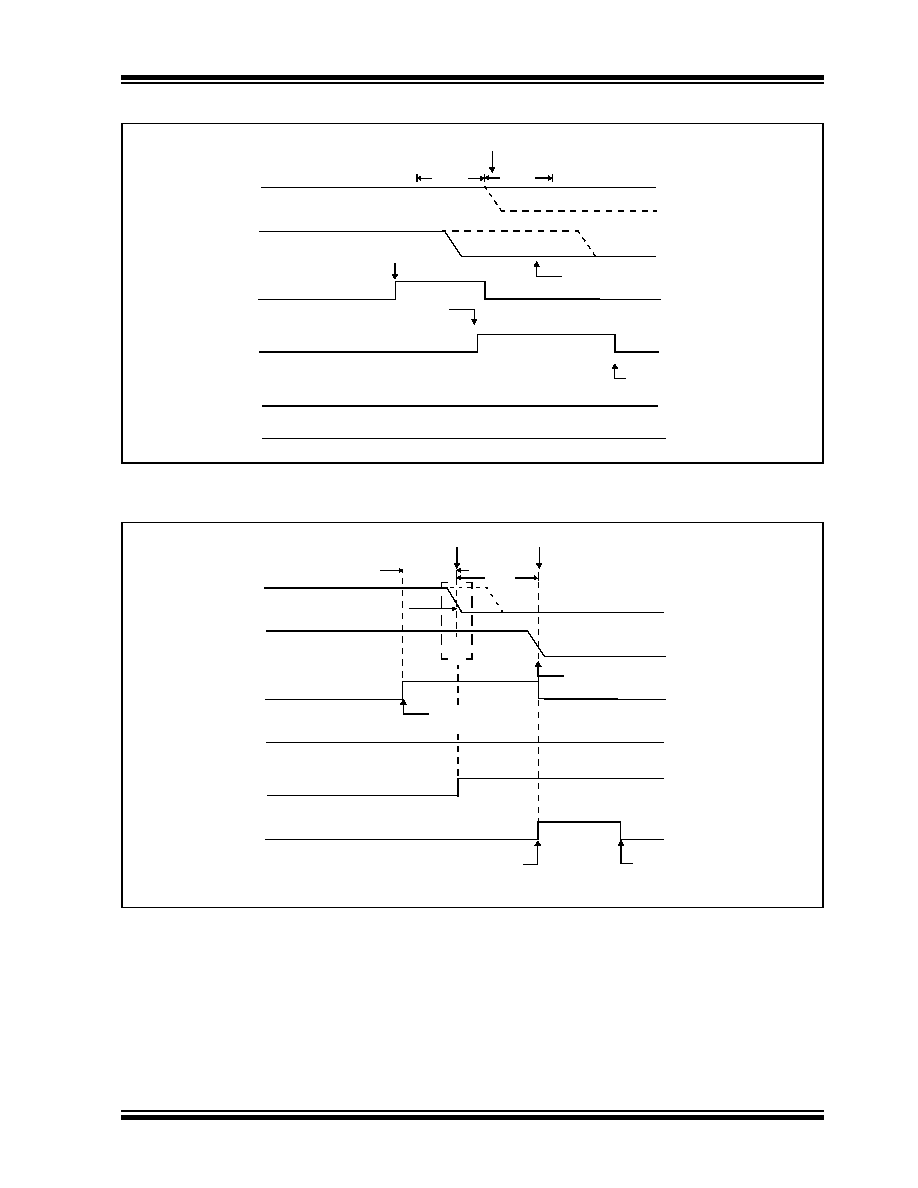

FIGURE 16-27:

BUS COLLISION DURING START CONDITION (SCL = 0)

FIGURE 16-28:

BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

SDA

SCL

SEN

bus collision occurs. Set BCLIF.

SCL = 0 before SDA = 0,

Set SEN, enable START

sequence if SDA = 1, SCL = 1

TBRG

SDA = 0, SCL = 1

BCLIF

S

SSPIF

Interrupt cleared

in software

bus collision occurs. Set BCLIF.

SCL = 0 before BRG time-out,

'0'

SDA

SCL

SEN

Set S

Set SEN, enable START

sequence if SDA = 1, SCL = 1

Less than TBRG

TBRG

SDA = 0, SCL = 1

BCLIF

S

SSPIF

S

Interrupts cleared

in software

Set SSPIF

SDA = 0, SCL = 1

SDA pulled low by other master.

Reset BRG and assert SDA.

SCL pulled low after BRG

Time-out

Set SSPIF

'0'

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF2539T-I/SO

IC MCU FLASH 12KX16 EE AD 28SOIC

PIC18LF4539T-I/PT

IC MCU FLASH 12KX16 EE AD 44TQFP

PIC16LF874AT-I/ML

IC MCU FLASH 4KX14 A/D 44QFN

PIC16F77T-E/ML

IC MCU FLASH 8KX14 A/D 44QFN

PIC16F874A-E/ML

IC MCU FLASH 4KX14 A/D 44QFN

PIC16F74T-I/ML

IC MCU FLASH 4KX14 A/D 44QFN

PIC16F77T-I/ML

IC MCU FLASH 8KX14 A/D 44QFN

PIC18F24K20-I/SS

IC PIC MCU FLASH 8KX16 28SSOP

相关代理商/技术参数

PIC18F4539T-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550EPT

制造商:Microchip Technology Inc 功能描述:

PIC18F4550-I/ML

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550-I/P

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550-I/PT

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550T-I/ML

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550T-I/PT

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4553-I/ML

功能描述:8位微控制器 -MCU 32KB FLSH 2048 RAM FSUSB 2.0 12B ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT